## **Dual Transistor**

# Synchronous Forward Controller

#### **FEATURES**

- High Voltage: Operation Up to 72V

- Synchronizable Operating Frequency and Output Switch Phase for Multiple Controller Systems

- Fixed Frequency Operation to 350kHz

- Adaptive and Adjustable Blanking

- Synchronous Rectifier Driver

- Local 1% Voltage Reference

- Undervoltage Lockout Protection with Hysteresis

- Input Overvoltage Protection

- Programmable Start Inhibit

- Transformer Primary Saturation Protection

- Optocoupler Feedback Support

- Soft-Start Control

#### **APPLICATIONS**

- Isolated Telecommunication Systems

- Personal Computers and Peripherals

- Lead Acid Battery Backup Systems

- Automotive and Heavy Equipment

## DESCRIPTION

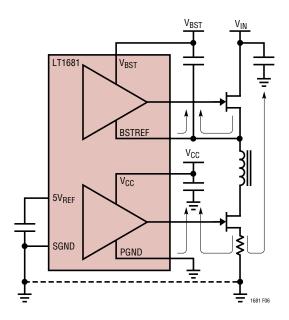

The LT®1681 controller simplifies the design of high power synchronous dual transistor forward DC/DC converters. The part employs fixed frequency current mode control and supports both isolated and nonisolated topologies. The IC drives external N-channel power MOSFETs and operates with input voltages up to 72V.

The LT1681's operating frequency is programmable and can be synchronized up to 350kHz. Switch phase is also controlled during synchronized operation to accommodate multiple converter systems. Internal logic guarantees 50% maximum duty cycle operation to prevent transformer saturation.

The LT1681 incorporates a soft-start feature that provides a controlled increase in supplied current during start-up and after an undervoltage lockout or overvoltage/overcurrent event.

The part is available in a 20-lead wide SO package to support high voltage pin-to-pin clearance.

7, LTC and LT are registered trademarks of Linear Technology Corporation.

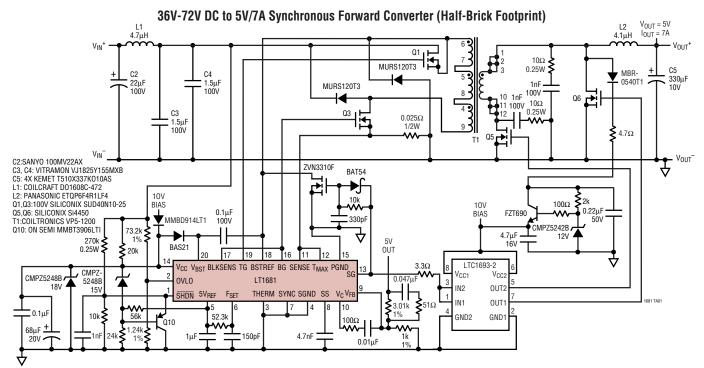

## TYPICAL APPLICATION

#### **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| ,                                                         |

|-----------------------------------------------------------|

| Supply Voltages                                           |

| Power Supply $(V_{CC})$ $-0.3V$ to 20V                    |

| Topside Supply $(V_{BST})$ $V_{BSTREF} - 0.3V$ to         |

| $V_{BSTREF} + 20V (V_{BST(MAX)} = 90V)$                   |

| Topside Reference Pin (V <sub>BSTREF</sub> ) –0.6V to 75V |

| Inp <u>ut Vo</u> ltages                                   |

| SHDN Pin0.3V to V <sub>CC</sub> + 0.3V                    |

| All Other Inputs $-0.3V$ to $5V_{REF} + 0.3V$             |

| Maximum Currents                                          |

| 5V <sub>REF</sub> Pin –85mA to 10mA                       |

| FSET Pin –2mA to 5mA                                      |

| All Other Inputs –2mA to 2mA                              |

| Operating Ambient Temperature Range                       |

| LT1681E (Note 4)40°C to 85°C                              |

| LT1681I –40°C to 85°C                                     |

| Storage Temperature Range65°C to 150°C                    |

| Lead Temperature (Soldering, 10 sec) 300°C                |

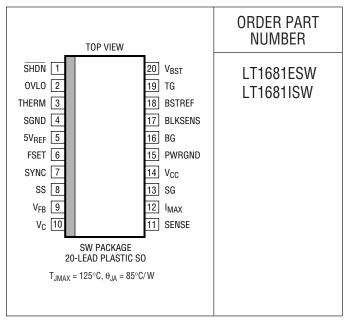

## PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

#### **ELECTRICAL CHARACTERISTICS**

The ullet denotes specifications which apply over the full operating temperature range, otherwise specifications are  $T_A=25^{\circ}C$ .  $V_{CC}=V_{BST}=12V$ ,  $V_{BSTREF}=0V$ ,  $V_{VC}=2V$ ,  $V_{FB}=V_{REF}=1.25V$ ,  $C_{TG}=C_{BG}=C_{SG}=1000pF$ .

| SYMBOL                | PARAMETER                                                | CONDITIONS                                    |   | MIN        | TYP          | MAX          | UNITS    |

|-----------------------|----------------------------------------------------------|-----------------------------------------------|---|------------|--------------|--------------|----------|

| Supply and Protection |                                                          |                                               |   |            |              |              |          |

| $V_{CC}$              | Operating Supply Voltage Range                           |                                               | • | 9          | 12           | 18           | V        |

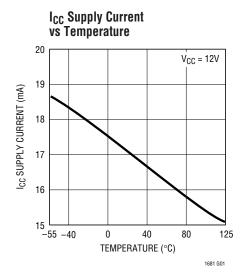

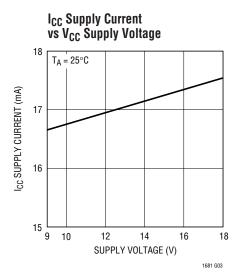

| I <sub>CC</sub>       | DC Active Supply Current                                 | (Note 2)                                      | • |            | 17           | 22<br>25     | mA<br>mA |

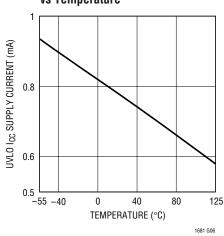

|                       | DC Active UVL Supply Current                             | $V_{\overline{SHDN}} > 1.35V$ , $V_{CC} = 8V$ | • |            | 800          | 1200         | μΑ       |

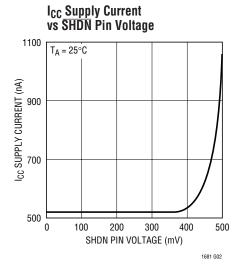

|                       | DC Standby Supply Current                                | V <sub>SHDN</sub> < 0.3V                      |   |            | 0.5          |              | μΑ       |

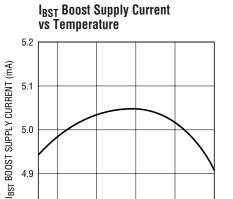

| I <sub>BST</sub>      | DC Active Supply Current                                 | TG Logic High (Note 2)                        | • |            | 5            | 8.5          | mA       |

|                       | DC Standby Supply Current                                | V <sub>SHDN</sub> < 0.3V                      |   |            | 0.1          |              | μΑ       |

| V <sub>SHDN</sub>     | Shutdown Rising Threshold                                |                                               | • | 1.15       | 1.25         | 1.35         | V        |

|                       | Shutdown Threshold Hysteresis                            |                                               | • | 100        | 150          | 200          | mV       |

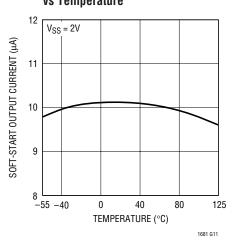

| I <sub>SS</sub>       | Soft-Start Charge Current                                | V <sub>SS</sub> = 2V                          | • | -14        | -10          | -6           | μΑ       |

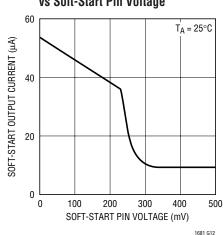

| $V_{SS}$              | Soft-Start Reset Threshold                               |                                               |   |            | 225          |              | mV       |

| V <sub>CCUVLO</sub>   | Undervoltage Lockout Threshold                           | Falling Edge<br>Rising Edge                   | • | 8.0<br>8.3 | 8.40<br>8.75 | 8.60<br>8.95 | V        |

|                       | Undervoltage Lockout Hysteresis                          |                                               | • | 0.25       | 0.35         |              | V        |

| V <sub>BSTUVLO</sub>  | Boost Undervoltage Lockout<br>(V <sub>BST</sub> -BSTREF) | Falling Edge<br>Rising Edge                   | • | 5.7<br>6.5 | 6.4<br>7.0   | 7.1<br>7.5   | V        |

|                       | Boost UVLO Hysteresis                                    |                                               | • | 0.3        | 0.6          |              | V        |

## **ELECTRICAL CHARACTERISTICS**

The ullet denotes specifications which apply over the full operating temperature range, otherwise specifications are  $T_A=25^{\circ}C$ .  $V_{CC}=V_{BST}=12V$ ,  $V_{BSTREF}=0V$ ,  $V_{VC}=2V$ ,  $V_{FB}=V_{REF}=1.25V$ ,  $C_{TG}=C_{BG}=C_{SG}=1000pF$ .

| SYMBOL                                    | PARAMETER                                                                         | CONDITIONS                                                               |   | MIN                 | TYP        | MAX                | UNITS    |

|-------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------|---|---------------------|------------|--------------------|----------|

| 5V Externa                                | al Reference                                                                      |                                                                          |   |                     |            |                    |          |

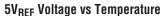

| V <sub>5VREF</sub>                        | 5V Reference Voltage                                                              | $0 \le (I_{5VREF} - I_{VC}) < 20mA$                                      | • | 4.85<br>4.80        | 5          | 5.10<br>5.15       | V        |

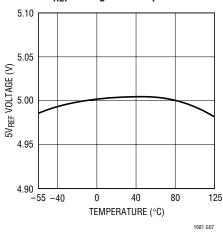

| I <sub>5VREFSC</sub>                      | Short-Circuit Current                                                             | Source, I <sub>VC</sub> = 0                                              | • | 20                  | 45         |                    | mA       |

| R <sub>5VREF</sub>                        | Output Impedance                                                                  | $0 \le (I_{5VREF} - I_{VC}) < 20mA$                                      |   |                     | 1          |                    | Ω        |

| Error Amp                                 |                                                                                   | 1                                                                        |   |                     |            |                    |          |

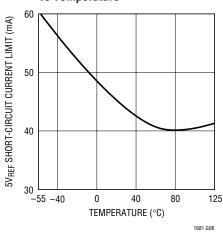

| V <sub>FB</sub>                           | Error Amplifier Reference Voltage                                                 | Measured at Feedback Pin                                                 | • | 1.242<br>1.225      | 1.250      | 1.258<br>1.265     | V        |

| I <sub>FB</sub>                           | Feedback Input Current                                                            | $V_{FB} = V_{REF}$                                                       |   |                     | -50        |                    | nA       |

| A <sub>V</sub>                            | Error Amplifier Voltage Gain                                                      |                                                                          |   |                     | 72         |                    | dB       |

| I <sub>VC</sub>                           | Error Amplifier Current Limit                                                     | Source<br>Sink                                                           | • | 10<br>0.5           | 25<br>1    |                    | mA<br>mA |

| $V_{VC}$                                  | Zero Current Output Voltage                                                       |                                                                          |   |                     | 1.4        |                    | V        |

|                                           | Maximum Output Voltage                                                            |                                                                          |   |                     | 3.2        |                    | V        |

| GBW                                       | Gain Bandwidth Product                                                            | (Note 3)                                                                 |   |                     | 1          |                    | MHz      |

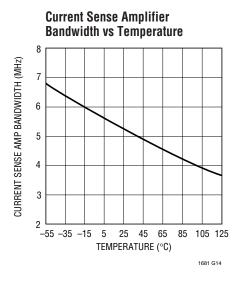

| Current Se                                | ense and Blanking                                                                 |                                                                          |   |                     |            |                    |          |

| A <sub>V</sub>                            | Amplifier DC Gain                                                                 |                                                                          |   |                     | 12         |                    | V/V      |

| I <sub>SENSE</sub>                        | Input Bias Current                                                                |                                                                          |   |                     | -275       |                    | μΑ       |

| V <sub>SENSE</sub>                        | Current Limit Threshold                                                           | Measured at SENSE Pin                                                    | • | 135<br>130          | 150        | 165<br>170         | mV<br>mV |

| $t_D$                                     | Current Sense to Switch Delay                                                     |                                                                          |   |                     | 175        |                    | ns       |

| $V_{BLKSENS}$                             | Blanking Input Threshold                                                          |                                                                          | • | 4.5                 | 5          | 5.5                | V        |

| I <sub>BLKSENS</sub>                      | Blanking Input Bias Current                                                       |                                                                          |   |                     | -2         |                    | μΑ       |

| t <sub>MIN</sub>                          | Switch Minimum On Time                                                            | V <sub>BLKSENS</sub> = V <sub>BG</sub> , Measured at BG Output           |   |                     | 250        |                    | ns       |

| I <sub>MAX</sub> Sens                     | e                                                                                 |                                                                          |   |                     |            |                    |          |

| I <sub>IMAX</sub>                         | Input Bias Current                                                                |                                                                          |   |                     | -250       |                    | μА       |

| V <sub>IMAX</sub>                         | I <sub>MAX</sub> Threshold (Rising Edge)<br>I <sub>MAX</sub> Threshold Hysteresis | Measured at I <sub>MAX</sub> Input<br>Measured at I <sub>MAX</sub> Input | • | 320                 | 360<br>140 | 400                | mV<br>mV |

| t <sub>P</sub>                            | I <sub>MAX</sub> Output Switch Disable Delay                                      | Measured at BG Output                                                    |   |                     | 130        |                    | ns       |

| THERM ar                                  | nd OVLO Fault Detectors                                                           |                                                                          |   |                     |            |                    |          |

| V <sub>THERM</sub> /<br>V <sub>OVLO</sub> | Threshold (Rising Edge)<br>Threshold Hysteresis                                   |                                                                          | • | 1.2<br>20           | 1.25<br>40 | 1.3<br>60          | V<br>mV  |

| t <sub>P</sub>                            | Fault Delay to Output Disable                                                     | 50mV Overdrive                                                           |   |                     | 650        |                    | ns       |

| Oscillator                                | and Synchronization Decoder                                                       |                                                                          |   |                     |            |                    |          |

| f <sub>OSC</sub>                          | Oscillator Frequency, Free Run                                                    | Measured at FSET Pin                                                     |   |                     |            | 700                | kHz      |

|                                           | Frequency Programming Error, Free Run                                             | f <sub>OSC</sub> ≤ 500kHz (Note 3)                                       | • | -10                 |            | 5                  | %        |

| I <sub>FSET</sub>                         | FSET Input Bias Current                                                           | FSET Charging, V <sub>FSET</sub> = 2V                                    |   |                     | 50         |                    | nA       |

| V <sub>SYNC</sub>                         | SYNC Logic High Input Threshold<br>SYNC Logic Low Input Threshold                 | Positive-Going Edge<br>Negative-Going Edge                               | • | 0.8                 | 1.4<br>1.4 | 2                  | V        |

| f <sub>SYNC</sub>                         | SYNC Frequency                                                                    |                                                                          | • | f <sub>0SC</sub> /2 |            | 350                | kHz      |

| t <sub>H, L</sub>                         | Maximum SYNC Pulse Width<br>(Logic High or Logic Low)                             | f <sub>OSC</sub> = Oscillator Free-Run Frequency                         |   |                     |            | 1/f <sub>OSC</sub> | S        |

#### **ELECTRICAL CHARACTERISTICS**

The ullet denotes specifications which apply over the full operating temperature range, otherwise specifications are  $T_A = 25^{\circ}C$ .  $V_{CC} = V_{BST} = 12V$ ,  $V_{BSTREF} = 0V$ ,  $V_{VC} = 2V$ ,  $V_{TS} = 0V$ ,  $V_{FB} = V_{REF} = 1.25V$ ,  $C_{TG} = C_{BG} = C_{SG} = 1000pF$ .

| SYMBOL             | PARAMETER                       | CONDITIONS            |   | MIN | TYP         | MAX | UNITS |

|--------------------|---------------------------------|-----------------------|---|-----|-------------|-----|-------|

| Output Drivers     |                                 |                       |   |     |             |     |       |

| V <sub>TG</sub>    | TG On Voltage<br>TG Off Voltage |                       | • | 11  | 11.5<br>0.1 | 0.5 | V     |

| t <sub>TGr/f</sub> | TG Rise/Fall Times              | 10% to 90%/90% to 10% |   |     | 35          |     | ns    |

| $V_{BG}$           | BG On Voltage<br>BG Off Voltage |                       | • | 11  | 11.5<br>0.1 | 0.5 | V     |

| t <sub>BGr/f</sub> | BG Rise/Fall Times              | 10% to 90%/90% to 10% |   |     | 35          |     | ns    |

| $V_{SG}$           | SG On Voltage<br>SG Off Voltage |                       | • | 11  | 11.5<br>0.1 | 0.5 | V     |

| t <sub>SGr/f</sub> | SG Rise/Fall Times              | 10% to 90%/90% to 10% |   |     | 35          |     | ns    |

| t <sub>SG-BG</sub> | SG to BG Enable Lag Time        | 4V On/Off Thresholds  | • | 80  | 150         | 300 | ns    |

| t <sub>TG-BG</sub> | TG to BG Enable Lag Time        | 4V On/Off Thresholds  |   |     | 100         |     | ns    |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** Supply current specification does not include external FET gate charge currents. Actual supply currents will be higher and vary with operating frequency, operating voltages and the type of external switch elements used. See Applications Information.

Note 3: Guaranteed but not tested.

**Note 4:** The LT1681E is guaranteed to meet performance specifications from  $0^{\circ}$ C to  $70^{\circ}$ C. Specifications over the  $-40^{\circ}$ C to  $85^{\circ}$ C operating temperature range are assured by design, characterization and correlation with statistical process controls. For guaranteed performance to specifications over the  $-40^{\circ}$ C to  $85^{\circ}$ C range, the LT1681I is available.

# TYPICAL PERFORMANCE CHARACTERISTICS

INEAR

## TYPICAL PERFORMANCE CHARACTERISTICS

UVLO I<sub>CC</sub> Supply Current vs Temperature

40

TEMPERATURE (°C)

80

125

1681 G04

4.8

-55 -40

5V<sub>REF</sub> Short-Circuit Current Limit vs Temperature

Error Amp Reference vs Temperature

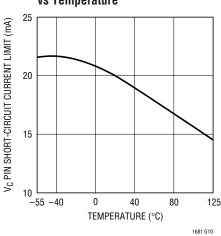

# V<sub>C</sub> Pin Short-Circuit Current Limit vs Temperature

Soft-Start Output Current vs Temperature

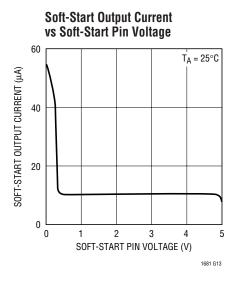

Soft-Start Output Current vs Soft-Start Pin Voltage

16811

#### TYPICAL PERFORMANCE CHARACTERISTICS

#### PIN FUNCTIONS

**SHDN** (**Pin 1**): Shutdown Pin. Pin voltages exceeding positive-going threshold of 1.25V enables the LT1681. 150mV of input hysteresis resists mode switching instability.

The SHDN pin can be controlled by either a logic-level input or with an analog signal. This shutdown feature is typically used for input supply undervoltage protection. A resistor divider from the converter input supply to the SHDN pin monitors that supply for control of system power-up sequencing, etc. All internal functions are disabled during shutdown.

**OVLO (Pin 2):** Overvoltage Shutdown Sense. Typically connected to input supply through a resistor divider. If pin voltage exceeds 1.25V, the LT1681 switching function is disabled to protect boosted circuitry from exceeding absolute maximum voltage. 40mV of input hysteresis resists mode switching instability. Exceeding the OVLO threshold also triggers soft-start reset, resulting in a graceful recovery from an input transient event.

**THERM (Pin 3):** System Thermal Shutdown. Auxiliary shutdown pin that is typically used for system thermal protection. If pin voltage exceeds 1.25V, the LT1681 switching function is disabled. 40mV of input hysteresis

resists mode switching instability. Exceeding the THERM threshold also triggers soft-start reset, resulting in a graceful recovery.

**SGND** (Pin 4): Signal Ground Reference. Careful board layout techniques must be used to prevent corruption of the signal ground reference. High current switching paths must be oriented on the converter ground plane such that currents to/from the switches do not affect the integrity of the LT1681 signal ground reference.

$5V_{REF}$  (Pin 5): 5V Local Reference. Allows connection of external loads up to 20mA DC. Typically bypassed with  $1\mu F$  ceramic capacitor to SGND. Reference output is current limit protected to a typical value of 45mA. If the load on the 5V reference exceeds the current limit value, LT1681 switching function is disabled and the soft-start function is reset.

**FSET (Pin 6):** Oscillator Timing Pin. Connect a resistor ( $R_{FSET}$ ) from the  $5V_{REF}$  pin to this pin and a capacitor ( $C_{FSET}$ ) from this pin to ground.

The LT1681 oscillator operates by monitoring the voltage on  $C_{FSET}$  as it is charged via  $R_{FSET}$ . When the voltage on the FSET pin reaches 2.5V, the oscillator rapidly discharges the capacitor with an average current of 0.8mA. Once the

LINEAR

1681f

#### PIN FUNCTIONS

voltage on the pin is reduced to 1.5V, the pin becomes high impedance and the charging cycle repeats. The oscillator operates at twice the switching frequency of the controller.

Oscillator frequency  $f_{OSC}$  can be approximated by the relation:

$$f_{OSC} \cong \left\{0.5 \bullet 10^{-6} + C_{FSET} \left[ \frac{R_{FSET}}{3} + \left( 8 \bullet 10^{-4} + \frac{2}{R_{FSET}} \right)^{\!-1} \right] \right\}^{-1}$$

**SYNC (Pin 7):** Oscillator Synchronization Input Pin with TTL-Level Compatible Input. The SYNC input signal (at the desired synchronized operating frequency) controls both the internal oscillator (running at twice the SYNC frequency) and the output switch phase. If the synchronization function is not desired, this pin may be shorted to ground.

The LT1681 internal oscillator drives a toggle flip-flop that assures ≤50% duty cycle operation during oscillator freerun. The oscillator, therefore, runs at twice the operating frequency of the converter. The SYNC input decoder incorporates a frequency doubling circuit for oscillator synchronization, resetting the internal oscillator on both the rising and falling edges of the input signal.

The SYNC input decoder also differentiates transition phase and forces the toggle flip-flop to phase-lock with the SYNC input. A transition to logic high on the SYNC input signal corresponds to the initiation of a new switching cycle (primary switches turning on pending current control) and a transition to logic low forces a primary switch off state. As such, the maximum operating duty cycle is equal to the duty cycle of the SYNC signal. The SYNC input can therefore be used to reduce the maximum duty cycle of the converter by reducing the duty cycle of the SYNC input.

**SS** (Pin 8): Soft-Start. Connect a capacitor ( $C_{SS}$ ) from this pin to ground.

The output voltage of the LT1681 error amplifier corresponds to the peak current sense amplifier output detected before resetting the switch outputs. The soft-start circuit forces the error amplifier output to a zero sense

current for start-up. A  $10\mu A$  current is forced from this pin onto an external capacitor. As the SS pin voltage ramps up, so does the LT1681 internally sensed current limit. This effectively forces the internal current limit to ramp from zero, allowing overall converter current to slowly increase until normal output regulation is achieved. This function reduces output overshoot on converter start-up. The soft-start function incorporates a  $1V_{BE}$  "dead zone" such that a zero current condition is maintained on the  $V_{C}$  pin until the SS pin rises to  $1V_{BF}$  above ground.

The SS pin voltage is reset to start-up condition during shutdown, undervoltage lockout and overvoltage or overcurrent events, yielding a graceful converter output recovery from these events.

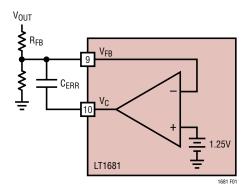

$V_{FB}$  (Pin 9): Error Amplifier Inverting Input. Typically connected to a resistor divider from the output and compensation components to the  $V_C$  pin.

The  $V_{FB}$  pin is the converter output voltage feedback node. Input bias current of ~50nA forces the pin high in the event of an open-feedback path condition. The error amplifier is internally referenced to 1.25V.

Values for the  $V_{OUT}$  to  $V_{FB}$  feedback resistor ( $R_{FB1}$ ) and the  $V_{FB}$  to ground resistor ( $R_{FB2}$ ) can be calculated to program converter output voltage ( $V_{OUT}$ ) via the following relation:

$$V_{OUT} = 1.25 \cdot (R_{FB1} + R_{FB2})/R_{FB2}$$

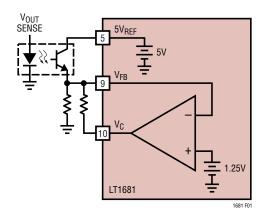

$V_C$  (Pin 10): Error Amplifier Output. The LT1681 error amplifier is a low impedance output inverting gain stage. The amplifier has ample current source capability to allow easy integration of isolation optocouplers that require bias currents up to 10mA. External DC loading of the  $V_C$  pin reduces the external current sourcing capacity of the  $V_{C}$  pin by the same amount as the load on the  $V_{C}$  pin.

The error amplifier is typically configured using a feedback RC network to realize an integrator circuit. This circuit creates the dominant pole for the converter regulation feedback loop. Integrator characteristics are dominated by the value of the capacitor connected from the  $V_{C}$  pin to the  $V_{FB}$  pin and the feedback resistor connected to the  $V_{FB}$  pin. Specific integrator characteristics can be configured to optimize transient response.

#### PIN FUNCTIONS

The error amplifier can also be configured as a transimpedance amplifier for use in secondary-side controller applications. (See Applications Information section for configuration and compensation details)

**SENSE (Pin 11):** Current Sense Amplifier (CSA) Noninverting Input. Current is monitored via a ground referenced current sense resistor, typically in series with the source of the bottom-side switch FET. Internal limit circuitry provides for a maximum peak value of 150mV across the sense resistor during normal operation.

I<sub>MAX</sub> (**Pin 12**): Primary Current Runaway Protection. The I<sub>MAX</sub> pin is used to detect primary-side switch currents and shuts down the primary switches if a current runaway condition is detected. The I<sub>MAX</sub> function is not disabled during the current sense blanking interval. The pin is typically connected to the primary bottom-side switch source and monitors switch current via a ground-referenced current sense resistor. If the pin voltage exceeds 360mV, LT1681 switching function is disabled in 130ns. Exceeding the I<sub>MAX</sub> threshold also triggers a soft-start reset, resulting in a graceful recovery from a current runaway event. For single-sense resistor systems, this pin can be shorted to SENSE for protection during the blanking interval or shorted to SGND if not used.

**SG** (**Pin 13**): Synchronous Switch Output Driver. This pin can be connected directly to the gate of the synchronous switch if small FETs are used ( $C_{GATE} < 5000 pF$ ), however, the use of a gate drive buffer is recommended for peak efficiencies.

The SG pin output is synchronized and out-of-phase with the BG output. The control timing of the SG output causes its transition to "lead" the primary switch path during turnon by 150ns.

$V_{CC}$  (Pin 14): IC Local Power Supply Input. Bypass with a capacitor at least 10 times greater than  $C_{5VREF}$  to PGND. The LT1681 incorporates undervoltage lockout that disables switching functions if  $V_{CC}$  is below 8.4V. The LT1681 supports operational  $V_{CC}$  power supply voltages from 9V to 18V (20V absolute maximum).

**PWRGND (Pin 15):** Output Driver Ground Reference. Connect through low impedance trace to  $V_{\text{IN}}$  decoupling capacitor.

**BG (Pin 16):** Bottom-Side Primary Switch/Forward Switch Output Driver. Pin can be connected directly to gate of primary bottom-side and forward switches if small FETs are used ( $C_{GATE}$  total < 5000pF), however, the use of a gate drive buffer is recommended for peak efficiencies.

The BG output is enabled at the start of each oscillator cycle in phase with the TG pin but is timed to "lag" the TG output during turn-on and "lead" the TG output during turn-off. These delays force the concentration of transitional losses onto the bottom-side primary switch.

**BLKSENS** (Pin 17): Blanking Sense Input. The current sense function (via SENSE pin) is disabled while the BLKSENS pin is below 5V. BLKSENS is typically connected to the gate of the bottom-side primary switch MOSFET.

**BSTREF (Pin 18):** V<sub>BST</sub> Supply Reference. Typically connects to source of topside external power FET switch.

**TG (Pin 19):** Topside (Boosted) Primary Output Driver. Pin can be connected directly to gate of primary topside switch if small FETs are used ( $C_{GATE} < 5000 pF$ ), however, the use of a gate drive buffer is recommended for peak efficiencies.

**V<sub>BST</sub> (Pin 20):** Topside Primary Driver Bootstrapped Supply. This "boosted" supply rail is referenced to the BSTREF pin.

Supply voltage is maintained by a bootstrap capacitor tied from the  $V_{BST}$  pin to the boosted supply reference (BSTREF) pin. The charge on the capacitor is refreshed each switch cycle through a Schottky diode connected from the  $V_{CC}$  supply (cathode) to the  $V_{BST}$  pin (anode). The bootstrap capacitor ( $C_{BOOST}$ ) must be at least 100 times greater than the total load capacitance on the TG pin. A capacitor in the range of  $0.1\mu F$  to  $1\mu F$  is generally adequate for most applications. The bootstrap diode must have a reverse-breakdown voltage greater than the converter  $V_{IN}$ . The LT1681 supports operational  $V_{BST}$  supply voltages up to 90V (absolute maximum) referenced to ground. Undervoltage lockout disables the topside switch until  $V_{BST}$ -BSTREF > 7.0V for start-up protection of the topside switch.

LINEAR

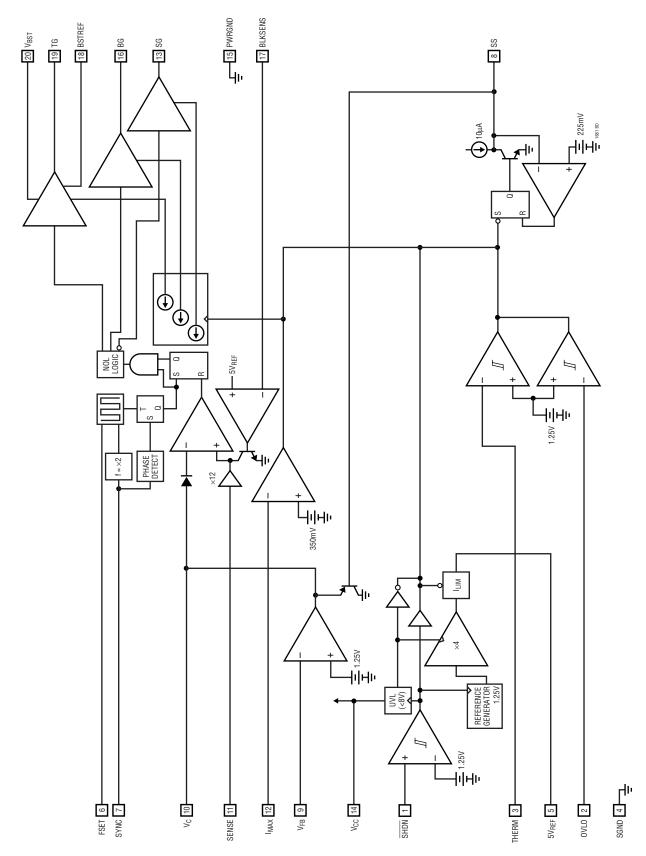

# **BLOCK DIAGRAM**

#### Overview

The LT1681 is a high voltage, high current synchronous regulator controller, optimized for use with dual transistor forward topologies. The IC uses a constant frequency, current mode architecture with internal logic that prevents operation over 50% duty cycle. A unique synchronization scheme allows the system clock to be synchronized up to an operational frequency of 350kHz, along with phase control for easy integration of multicontroller systems. A local precision 5V supply is available for external support circuitry and can be loaded up to 20mA.

Internal fault detection circuitry disables switching when a variety of system faults are detected such as: input supply overvoltage or undervoltage faults, excessive system temperature, transformer primary-side saturation and local supply overcurrent conditions. The LT1681 has a current limit soft-start feature that gradually increases the current drive capability of a converter system to yield a smooth start-up with minimal overshoot. The soft-start circuitry is also used for smooth recoveries from system fault conditions.

External FET switches are employed for the switch elements, and hearty switch drivers allow implementation of high current designs. An adaptive blanking scheme built into the LT1681 allows for correct current-sense blanking regardless of switch size and even while using external switch drive buffers. The LT1681 employs a voltage output error amplifier, providing superior integrator linearity and allowing easy high bandwidth integration of optocoupler feedback for fully isolated solutions.

#### Theory of Operation (See Block Diagram)

The LT1681 senses the output voltage of its associated converter via the  $V_{FB}$  pin. The difference between the voltage on this pin and an internal 1.25V reference is amplified to generate an error voltage on the  $V_{C}$  pin, which is used as a threshold for the current sense comparator. The current sense comparator gets its information from the SENSE pin, which monitors the voltage drop across an external current sense resistor. When the detected switch current increases to the level corresponding to the error

voltage on the  $V_{\text{C}}$  pin, the switches are disabled until the next switch cycle.

During normal operation, the LT1681 internal oscillator runs at twice the switching frequency. The oscillator output toggles a T flip-flop, generating a 50% duty cycle pulse that is used internally as the system clock for the IC. When the output of this flip-flop transitions high, the primary switches are enabled. The primary-side switches stay enabled until the transformer primary current, sensed via the SENSE pin, connected to a ground-referenced resistor in series with the bottom-side switch FET, is sufficient to trip the current sense comparator and, in turn, reset the RS latch. When the RS latch resets, the primary switches are disabled and the synchronous switch is enabled. The adaptive blanking circuit senses the bottomside gate voltage via the BLKSENS pin and prevents current sensing until the FET is fully enabled, preventing false triggering due to a turn-on transition glitch. If the current comparator threshold is not obtained when the flip-flop output transitions low, the RS latch is bypassed and the primary switches are disabled until the next flipflop output transition, forcing a maximum switch duty cycle less than 50%.

# System Fault Detection—The General Fault Condition (GFC)

The LT1681 contains circuitry for detecting internal and system faults. Detection of a fault triggers a "general fault condition" or GFC. When a GFC is detected, the LT1681 disables switching and discharges the soft-start capacitor. When the GFC subsides, the LT1681 initiates a startup cycle via the soft-start circuitry to assure a graceful recovery. Recovery from a GFC is gated by the soft-start capacitor discharge. The capacitor must be discharged to a threshold of 225mV before the GFC can be concluded. As the zero output current threshold of the SS pin is typically a transistor V<sub>BE</sub>, or 0.7V, latching the GFC until a 225mV threshold is achieved assures a zero output current state is obtained in the event of a short-duration fault. A GFC is also triggered during a system state change event, such as entering shutdown mode, to prevent any mode transition abnormalities.

Events that trigger a GFC are:

- a) Exceeding the current limit of the 5V<sub>RFF</sub> pin

- b) Detecting an undervoltage condition on V<sub>CC</sub>

- c) Detecting an undervoltage condition on 5V<sub>RFF</sub>

- d) Pulling the SHDN pin below the shutdown threshold

- e) Exceeding the I<sub>MAX</sub> pin threshold

- f) Exceeding the 1.25V fault detector threshold on either the OVLO or THERM pins

The OVLO and THERM pins are used to directly trigger a GFC. If either of these pins are not used, they can be disabled by connecting the pin to SGND. The intention of the OLVO pin is to allow monitoring of the input supply to protect from an overvoltage condition. Monitoring of system temperature (THERM) is possible through use of a resistor divider using a thermistor as a resistor divider component. The  $5V_{REF}$  pin can provide the precision supply required for these applications. When these fault detection circuits are disabled during shutdown or  $V_{CC}$  pin UVLO conditions, a reduction in OVLO and THERM pin input impedance to ground will occur. To prevent excessive pin input currents, low impedance pull-up devices must not be used on these pins.

#### **Undervoltage Lockout**

The LT1681 maintains a low current operational mode when an undervoltage condition is detected on the  $V_{CC}$  supply pin, or when  $V_{CC}$  is below the undervoltage lockout (UVLO) threshold. During a UVLO condition on the  $V_{CC}$  pin, the LT1681 disables all internal functions with the exception of the shutdown and UVLO circuitry. The external  $5V_{REF}$  supply is also disabled during this condition. Disabling of all switching control circuity reduces the LT1681 supply current to <1mA, simplifying integration of trickle charging in systems that employ output feedback supply generation.

The function of the high side switch output (TG) is also gated by UVLO circuitry monitoring the bootstrap supply (V<sub>BST</sub>-BSTREF). Switching of the TG pin is disabled until the voltage across the bootstrap supply is greater than 7.4V. This helps prevent the possibility of forcing the high side switch into a linear operational region, potentially

causing excessive power dissipation due to inadequate gate drive during start-up.

#### **Error Amplifier Configurations**

The converter output voltage information is fed back to the LT1681 onto the  $V_{FB}$  pin where it is transformed into an output current control voltage by the error amplifier. The error amplifier is generally configured as an integrator and is used to create the dominant pole for the main converter feedback loop. The LT1681 error amplifier is a true high gain voltage amplifier. The amplifier noninverting input is internally referenced to 1.25V; the inverting input is the  $V_{FB}$  pin and the output is the  $V_{C}$  pin. Because both low frequency gain and integrator frequency characteristics can be controlled with external components, this amplifier allows far greater flexibility and precision compared with use of a transconductance error amplifier.

In a nonisolated converter configuration where a resistor divider is used to program the desired output voltage, the error amplifier can be configured as a simple active integrator, forming the system dominant pole (see Figure 1). Placing a capacitor  $C_{ERR}$  from the  $V_{FB}$  pin to the  $V_{C}$  pin will set the single-pole crossover frequency at  $(2\pi R_{FB}C_{ERR})^{-1}$ . Additional poles and zeros can be added by increasing the complexity of the RC network.

Figure 1. Nonisolated Error Amp Configuration

Another common error amplifier configuration is for optocoupler use in fully isolated converters with secondary-side control (see Figure 2). In such a system, the dominant pole for the feedback loop is created at the secondary-side controller, so the error amplifier needs only to

translate the optocoupler information. The bandwidths of the optocoupler and amplifier should be as high as possible to simplify system compensation. This high bandwidth operation is accomplished by using the error amplifier as a transimpedance amplifier, with the optocoupler transistor emitter providing feedback information directly into the  $V_{FB}$  pin. A resistor from  $V_{FB}$  to ground provides the DC bias condition for the optocoupler. Connecting the optocoupler transistor collector to the local  $5V_{REF}$  supply reduces Miller capacitance effects and maximizes the bandwidth of the optocoupler. Higher optocoupler current also means higher bandwidth, and the  $5V_{REF}$  supply can provide collector currents up to 10mA.

Figure 2. Optocoupler High BW Configuration

# Oscillator Frequency Programming and Synchronization

The LT1681 internal oscillator runs at twice the system switching frequency. The oscillator output toggles a T flipflop, generating a 50% duty cycle pulse that is used internally as the system clock for the IC. Free-run frequency for the internal oscillator is programmed via an RC timing network connected to the FSET pin. A pull-up resistor  $R_{FSET}$ , connected from the  $5V_{REF}$  pin to FSET, provides current to charge a timing capacitor  $C_{FSET}$  connected from the FSET pin to ground. The oscillator operates by allowing  $R_{FSET}$  to charge  $C_{FSET}$  up to 2.5V at which point  $R_{FSET}$  is pulled back toward ground by a 2.5k resistor internal to the LT1681. When the voltage across  $C_{FSET}$  is pulled down to 1.5V, the FSET pin becomes high impedance, once again allowing  $R_{FSET}$  to charge  $C_{FSET}$ .

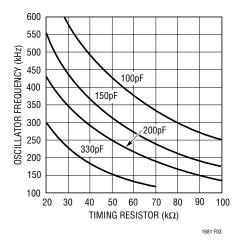

Figure 3 is a plot of oscillator frequency vs  $C_{FSET}$  and  $R_{FSET}$ . Typical values for 300kHz operation (150kHz system frequency) are  $C_{FSET} = 150pF$  and  $R_{FSET} = 51k$ .

Figure 3. Oscillator Frequency vs Timing Components

Due the relatively fast fall time of the oscillator waveform, the FSET pin is held at its 1.5V threshold by an internal low-impedance clamp to reduce undershoot error. If this pin is externally forced low for any reason, external current limiting is required to prevent damage to the LT1681. Continuous source current from the FSET pin should not exceed 1mA. Putting a 2k resistor in series with any low impedance pull-down device will assure proper function and protect the IC from damage.

#### **Oscillator Synchronization**

Synchronization of the LT1681 system clock is accomplished by driving a TTL level logic pulse train at the desired system switching frequency into the SYNC pin. In order to assure proper synchronization, each phase of the synchronization signal must be less then an oscillator free-run cycle.

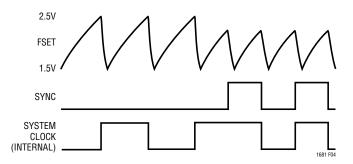

The SYNC input pulse controls the phasing as well as the frequency of controller switching. The SYNC circuit functions by forcing the phase of the oscillator output flip-flop to match the phase of the SYNC pulse and prematurely ending the oscillator charge cycle on each transition edge. At the SYNC low-to-high transition, the LT1681 starts a switch-on cycle and the minimum switch-off period is forced during the SYNC logic low period. Because the SYNC logic low period corresponds directly

to the minimum off time, the converter maximum duty cycle can be forced using the SYNC input. For example, a 30% duty cycle SYNC pulse forces 30% maximum duty cycle operation for the converter. Because the logic low pulse width exceeds the logic high pulse width in <50% duty cycle operation, the oscillator free-run cycle time must be programmed to exceed the logic low duration.

Figure 4. Oscillator/SYNC Waveforms

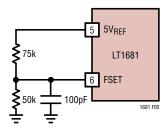

It is also possible to run the LT1681 in a SYNC-only mode by disabling the oscillator completely. Connecting a resistor divider from the  $5V_{REF}$  pin to the FSET pin, forcing a voltage within the charge range of 1.5V to 2.5V, will allow the oscillator to follow the SYNC input exclusively with no provision for free-run. Setting values to force a voltage as close to 2V as possible is recommended.

Figure 5. Oscillator Connection for Sync-Only Mode Operation

#### Shutdown

The LT1681 SHDN pin will support TTL and CMOS logic signals and also analog inputs. The SHDN pin turn-on (rising) threshold is 1.25V with 150mV of hysteresis. A common use of the SHDN pin is for undervoltage detection on the input supply. Driving the SHDN pin with a resistor divider connected from the input supply to ground will prevent switching until the desired input supply voltage is achieved.

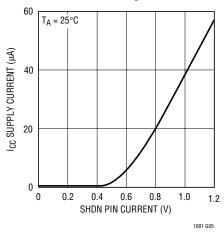

The LT1681 enters an ultralow current shutdown mode when the  $\overline{SHDN}$  pin is below 350mV. During this mode, total supply current drops to a typical value of less than 1 $\mu$ A. When  $\overline{SHDN}$  rises above 350mV, the IC will draw increasing amounts of supply current until just before the 1.25V turn-on threshold is achieved, when the typical supply current reaches 60 $\mu$ A.

The shutdown function can be disabled by connecting the  $\overline{SHDN}$  pin to  $V_{CC}$ . This pin is internally clamped to 2.5V through a 20k series input resistance and can therefore draw almost 1mA when tied directly to the  $V_{CC}$  supply. This additional current can be minimized by making the connection through an external series resistor (100k is typically used).

#### Soft-Start

The LT1681 current control pin ( $V_C$ ) limits sensed current to zero at voltages less than 1.4V through full current limit at  $V_C = 3.2V$ , yielding 1.8V over the full regulation range. The voltage on the  $V_C$  pin is internally forced to be less than or equal to SS + 0.7V. As such, the SS pin has a "dead zone" between 0V and 0.7V, where a zero sensed current condition is maintained. At SS voltages above 0.7V, the sensed current limit threshold on pin  $V_C$  may rise as needed up to the SS maintained current limit value. Once the SS pin rises to the  $V_C$  pin maximum value less 0.7V, or 2.5V, the SS circuit has no effect.

The SS pin sources a typical current of  $10\mu A$ . Placing a capacitor ( $C_{SS}$ ) from the SS pin to ground will cause the voltage on the SS pin to ramp up at a controlled rate, allowing a graceful increase of maximum converter output current during a start-up condition. The start-up delay time to full available current limit is:

$$t_{SS} = 2.5 \cdot 10^5 \cdot C_{SS}$$

(sec)

The LT1681 internally pulls the SS pin below the zero current threshold during any fault condition to assure graceful recovery. The SS circuit also acts as a fault control latch to assure a full-range recovery from a short duration fault. Once a fault condition is detected, the LT1681 will suspend switching until the SS pin has discharged to approximately 225mV.

#### Layout Considerations—Grounding

The LT1681 is typically used in high current converter designs that involve substantial switching transients. The switch drivers on the IC are designed to drive large capacitances and, as such, generate significant transient currents. Careful consideration must be made regarding input and local power-supply bypassing to avoid corrupting the ground references used by the error amplifier and current sense circuitry.

Effective grounding of the two-transistor synchronous forward topology where the LT1681 is used is inherently difficult. The situation is complicated further by the number of bypass elements that must be considered.

Typically, high current paths and transients from the input supply and any local drive supplies must be kept isolated from SGND, to which sensitive circuits such as the error amp reference and the current sense circuits, as well as the local  $5V_{REF}$  supply, are referred. By virtue of the topologies used in LT1681 applications, the large currents from the primary switches, as well as the switch drive transients,

pass through the sense resistor to ground. This defines the ground connection of the sense resistor as the reference point for both SGND and PGND. In nonisolated applications where SGND is the output reference, we now have a condition where every bypass capacitor in the converter is referenced to the same point.

Effective grounding can be achieved by considering the return current paths from the sense resistor to each respective bypass capacitor. Don't be tempted to run small traces to separate the grounds. A power ground plane is important as always in high-power converters, but bypass elements must be oriented such that transient currents in the return paths of  $V_{IN}$  and  $V_{CC}$  do not mix. Care must be taken to keep these transients away from the SGND reference. An effective approach is to use a 2-layer ground plane, reserving an entire layer for SGND. The  $5V_{REF}$  and non-isolated converter output bypasses can then be directly connected to the SGND plane.

Figure 6. High Current Transient Return Paths

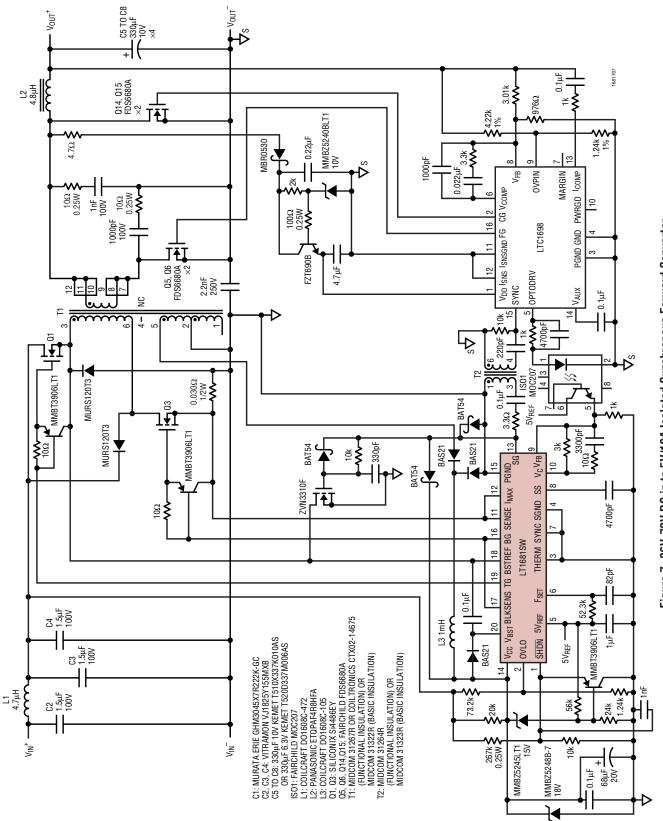

Figure 7. 36V-72V DC in to 5V/10A Isolated Synchronous Forward Converter

LINEAR TECHNOLOGY

1681f

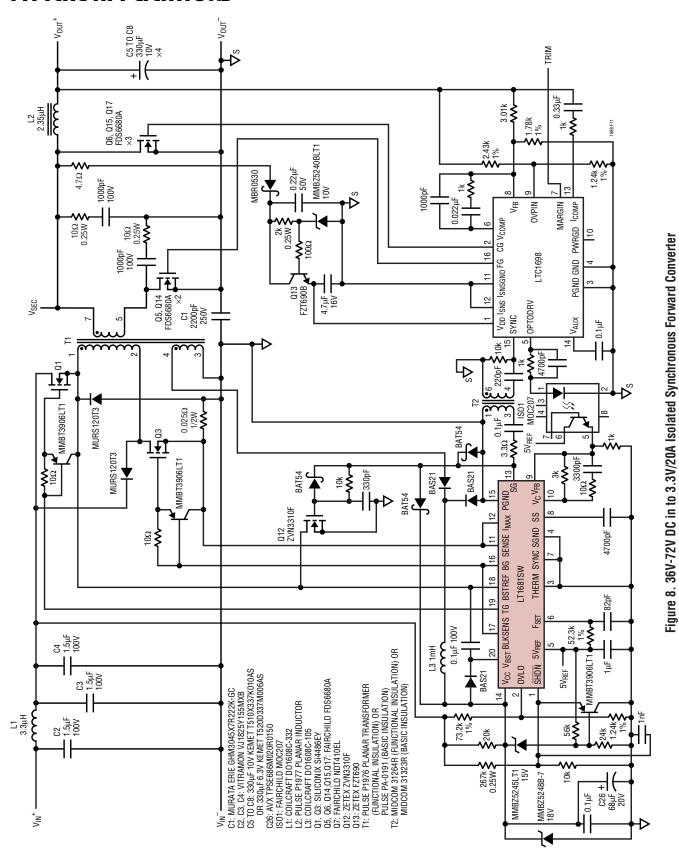

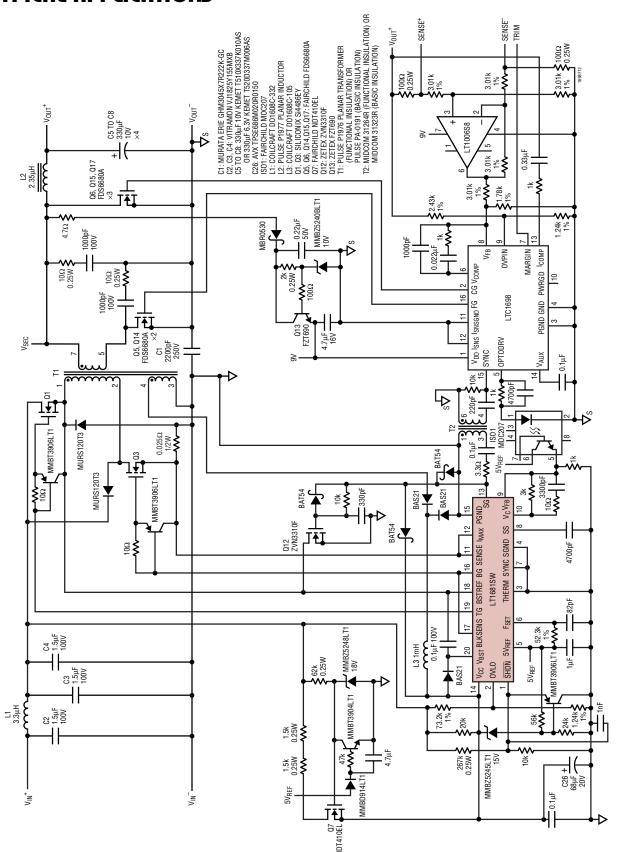

Figure 9. 36V-72V DC in to 3.3V/20A Isolated Synchronous Forward Converter with Fast Start and Differential Sense

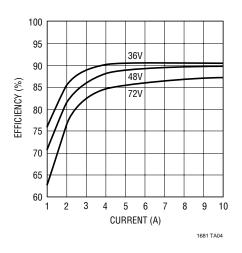

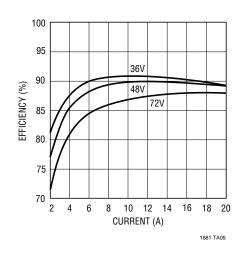

LT1681/LTC1698 36V-72V  $\ensuremath{V_{\text{IN}}}$  to 5V/10A Module (See Figure 7 for Application Schematic)

LT1681/LTC1698 36V-72V  $\mbox{V}_{\mbox{\scriptsize IN}}$  to 3.3V/20A Module (See Figure 9 for Application Schematic)

#### LT1681/LTC1698 Isolated 5V/10A Converter Efficiency vs Load Current

#### LT1681/LTC1698 Isolated 3.3V/20A Converter Efficiency vs Load Current

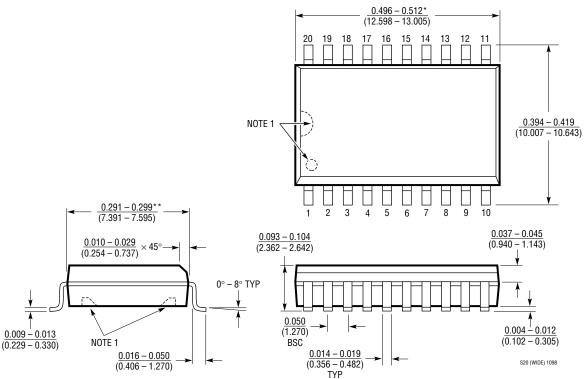

## PACKAGE DESCRIPTION

#### SW Package 20-Lead Plastic Small Outline (Wide .300 Inch)

(Reference LTC DWG # 05-08-1620)

#### NOTE:

- PIN 1 IDENT, NOTCH ON TOP AND CAVITIES ON THE BOTTOM OF PACKAGES ARE THE MANUFACTURING OPTIONS.

THE PART MAY BE SUPPLIED WITH OR WITHOUT ANY OF THE OPTIONS

- \*DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

- \*\*DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

## **RELATED PARTS**

| PART NUMBER           | DESCRIPTION                                                                                             | COMMENTS                                                                                                                                               |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LT1158                | Half-Bridge N-Channel MOSFET Driver                                                                     | Current Limit Protection, 100% of Duty Cycle                                                                                                           |  |  |

| LT1160                | Half-Bridge N-Channel MOSFET Driver                                                                     | Up to 60V Input Supply, No Shoot-Through                                                                                                               |  |  |

| LT1162                | Dual Half-Bridge N-Channel MOSFET Driver                                                                | V <sub>IN</sub> to 60V, Good for Full-Bridge Applications                                                                                              |  |  |

| LT1336                | Half-Bridge N-Channel MOSFET Driver                                                                     | Smooth Operation at High Duty Cycle (95% to 100%)                                                                                                      |  |  |

| LT1339                | High Power Synchronous DC/DC Controller                                                                 | 60V Dual N-Channel MOSFET Controller                                                                                                                   |  |  |

| LTC <sup>®</sup> 1530 | High Power Step-Down Switching Regulator Controller                                                     | Excellent for 5V to 3.x Up to 50A                                                                                                                      |  |  |

| LTC1622               | 550kHz Step-Down Controller                                                                             | 8-Pin MSOP; Synchronizable; Soft-Start; Current Mode                                                                                                   |  |  |

| LTC1625/LTC1775       | No R <sub>SENSE</sub> ™ Current Mode Synchronous Step-Down Controller                                   | 97% Efficiency; No Sense Resistor; 16-Pin SSOP                                                                                                         |  |  |

| LTC1628-PG            | Dual, 2-Phase Synchronous Step-Down Controller                                                          | Power Good Output; Minimum Input/Output Capacitors; $3.5V \le V_{IN} \le 36V$                                                                          |  |  |

| LTC1628-SYNC          | Dual, 2-Phase Synchronous Step-Down Controller                                                          | Synchronizable 150kHz to 300kHz, V <sub>IN</sub> to 36V                                                                                                |  |  |

| LT1680                | High Power DC/DC Current Mode Step-Up Controller                                                        | High Side Current Sense, Up to 60V Input                                                                                                               |  |  |

| LTC1698               | Secondary Synchronous Rectifier Controller                                                              | Use with the LT1681, Isolated Power Supplies, Contains<br>Voltage Margining, Optocoupler Driver, Synchronization Circuit<br>with the Primary Side      |  |  |

| LTC1709-7             | High Efficiency, 2-Phase Synchronous Step-Down Controller with 5-Bit VID                                | Up to 42A Output; 0.925V ≤ V <sub>OUT</sub> ≤ 2V                                                                                                       |  |  |

| LTC1709-8             | High Efficiency, 2-Phase Synchronous Step-Down Controller                                               | Up to 42A Output; VRM 8.4; $1.3V \le V_{OUT} \le 3.5V$                                                                                                 |  |  |

| LTC1735               | High Efficiency, Synchronous Step-Down Controller                                                       | Burst Mode® Operation; 16-Pin Narrow SSOP; $3.5V \le V_{IN} \le 36V$                                                                                   |  |  |

| LTC1736               | High Efficiency, Synchronous Step-Down Controller with 5-Bit VID                                        | Mobile VID; $0.925V \le V_{OUT} \le 2V$ ; $3.5V \le V_{IN} \le 36V$                                                                                    |  |  |

| LTC1772               | ThinSOT™ Step-Down Controller                                                                           | Current Mode; 550kHz; Very Small Solution Size                                                                                                         |  |  |

| LTC1773               | Synchronous Step-Down Controller                                                                        | Up to 95% Efficiency, 550kHz, 2.65V $\leq$ V <sub>IN</sub> $\leq$ 8.5V, 0.8V $\leq$ V <sub>OUT</sub> $\leq$ V <sub>IN</sub> , Synchronizable to 750kHz |  |  |

| LTC1778               | Wide Operating Range, No R <sub>SENSE</sub> Step-Down Controller                                        | GN16-Pin, 0.8V FB Reference                                                                                                                            |  |  |

| LTC1874               | Dual, Step-Down Controller                                                                              | Current Mode; 550kHz; Small 16-Pin SSOP, V <sub>IN</sub> < 9.8V                                                                                        |  |  |

| LTC1876               | 2-Phase, Dual Synchronous Step-Down Controller with Step-Up Regulator                                   | $3.5V \le V_{IN} \le 36V$ , Power Good Output, 300kHz Operation                                                                                        |  |  |

| LTC1922-1             | Synchronous Phase Modulated Full-Bridge Controller                                                      | 50W to 2kW Power Supply Design, Adaptive Direct Sense ZVS                                                                                              |  |  |

| LTC1929               | 2-Phase 42A Synchronous Controller                                                                      | Minimizes $C_{IN}$ and $C_{OUT}$ , $4V \le V_{IN} \le 36V$ , $300kHz$                                                                                  |  |  |

| LTC3714               | Intel Compatible, Wide Operating Range, No R <sub>SENSE</sub> Step-Down Controller with Internal Op Amp | G28 Package, V <sub>OUT</sub> = 0.6V to 1.75V 5-Bit Mobile VID,<br>Active Voltage Positioning I <sub>MVP2</sub> , V <sub>IN</sub> to 36V               |  |  |

| LTC3716               | High Efficiency, 2-Phase Synchronous Step-Down Controller with 5-Bit Mobile VID                         | $V_{OUT}$ = 0.6V to 1.75V, Active Voltage Positioning I <sub>MVP2</sub> , $V_{IN}$ to 36V                                                              |  |  |

No R $_{\rm SENSE}$  and ThinSOT are trademarks of Linear Technology Corporation. Burst Mode is a registered trademark of Linear Technology Corporation.